# Advances in COMPUTERS Volume 69 Architectural Issues

## Edited by MARVIN V. ZELKOWITZ

Advances in COMPUTERS VOLUME 69 This page intentionally left blank

# Advances in COMPUTERS

## **Architectural Issues**

## EDITED BY MARVIN V. ZELKOWITZ

Department of Computer Science and Institute for Advanced Computer Studies University of Maryland College Park, Maryland

VOLUME 69

AMSTERDAM • BOSTON • HEIDELBERG • LONDON • NEW YORK • OXFORD PARIS • SAN DIEGO • SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO Academic Press is an imprint of Elsevier

Academic Press is an imprint of Elsevier 84 Theobald's Road, London WC1X 8RR, UK Radarweg 29, PO Box 211, 1000 AE Amsterdam, The Netherlands The Boulevard, Langford Lane, Kidlington, Oxford OX5 1GB, UK 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA 525 B Street, Suite 1900, San Diego, CA 92101-4495, USA

First edition 2007

Copyright © 2007 Elsevier Inc. All rights reserved

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means electronic, mechanical, photocopying, recording or otherwise without the prior written permission of the publisher

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone (+44) (0) 1865 843830; fax (+44) (0) 1865 853333; email: permissions@elsevier.com. Alternatively you can submit your request online by visiting the Elsevier web site at http://elsevier.com/locate/permissions, and selecting *Obtaining permission to use Elsevier material*

Notice

No responsibility is assumed by the publisher for any injury and/or damage to persons or property as a matter of products liability, negligence or otherwise, or from any use or operation of any methods, products, instructions or ideas contained in the material herein. Because of rapid advances in the medical sciences, in particular, independent verification of diagnoses and drug dosages should be made

ISBN-13: 978-0-12-373745-8

ISSN: 0065-2458

For information on all Academic Press publications visit our website at books.elsevier.com

Printed and bound in USA

$07 \ 08 \ 09 \ 10 \ 11 \quad 10 \ 9 \ 8 \ 7 \ 6 \ 5 \ 4 \ 3 \ 2 \ 1$

## Contents

| CONTRIBUTORS |  |   |  |  |  |  |  |  |  |  | • |   |  |  |  |  | ix   |

|--------------|--|---|--|--|--|--|--|--|--|--|---|---|--|--|--|--|------|

| PREFACE      |  | • |  |  |  |  |  |  |  |  | • | • |  |  |  |  | xiii |

## The Architecture of Efficient Multi-Core Processors: A Holistic Approach

#### Rakesh Kumar and Dean M. Tullsen

| Introduction                                                     | 3                                 |

|------------------------------------------------------------------|-----------------------------------|

| The Move to Multi-Core Processors                                | 5                                 |

| Holistic Design for Adaptability: Heterogeneous Architectures    | 9                                 |

| Amortizing Overprovisioning through Conjoined Core Architectures | 45                                |

| Holistic Design of the Multi-Core Interconnect                   | 62                                |

| Summary and Conclusions                                          | 81                                |

| Acknowledgements                                                 | 82                                |

| References                                                       | 82                                |

|                                                                  | The Move to Multi-Core Processors |

## **Designing Computational Clusters for Performance and Power**

## Kirk W. Cameron, Rong Ge, and Xizhou Feng

| 1. | Introduction                          | 90  |

|----|---------------------------------------|-----|

| 2. | Background                            | 91  |

| 3. | Single Processor System Profiling     | 96  |

| 4. | Computational Cluster Power Profiling | 98  |

| 5. | Low Power Computational Clusters      | 112 |

| 6. | Power-Aware Computational Clusters    | 125 |

| 7. | Conclusions                           | 149 |

|    | References                            | 149 |

|    |                                       |     |

#### CONTENTS

## **Compiler-Assisted Leakage Energy Reduction for Cache Memories**

#### Wei Zhang

| 1. | Introduction                                                  | 156 |

|----|---------------------------------------------------------------|-----|

| 2. | Related Work                                                  | 159 |

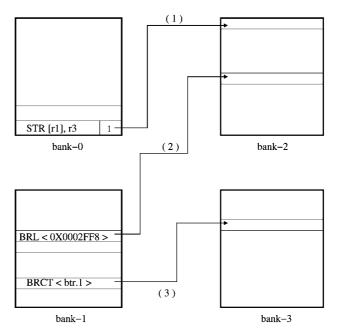

| 3. | Static Next Sub-Bank Prediction for Drowsy Instruction Caches | 161 |

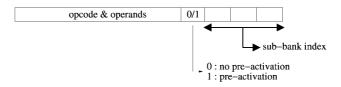

| 4. | Compiler-Assisted Loop-Based Data Cache Leakage Reduction     | 170 |

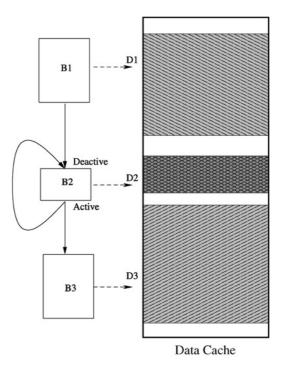

| 5. | Evaluation Methodology                                        | 172 |

| 6. | Conclusion                                                    | 186 |

|    | References                                                    | 187 |

### **Mobile Games: Challenges and Opportunities**

Paul Coulton, Will Bamford, Fadi Chehimi, Reuben Edwards, Paul Gilbertson, and Omer Rashid

| 1. | Introduction     |

|----|------------------|

| 2. | Challenges       |

| 3. | Opportunities    |

| 4. | Conclusions      |

|    | Acknowledgements |

|    | References       |

## Free/Open Source Software Development: Recent Research Results and Methods

#### Walt Scacchi

| 1. | Introduction                                                          | 244 |

|----|-----------------------------------------------------------------------|-----|

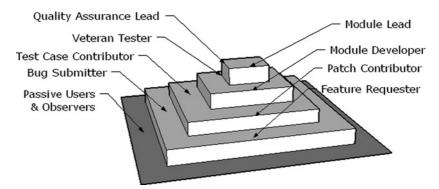

| 2. | Individual Participation in FOSSD Projects                            | 248 |

| 3. | Resources and Capabilities Supporting FOSSD                           | 253 |

| 4. | Cooperation, Coordination, and Control in FOSS Projects               | 260 |

| 5. | Alliance Formation, Inter-project Social Networking and Community De- |     |

|    | velopment                                                             | 265 |

| 6. | FOSS as a Multi-project Software Ecosystem                            | 270 |

| 7. | FOSS as a Social Movement                                             | 274 |

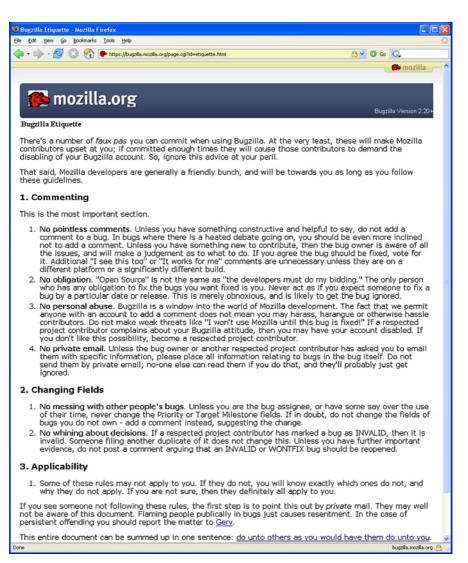

| 8. | Research Methods for Studying FOSS                                    | 277 |

| 9. | Discussion                                                            | 284 |

#### CONTENTS

| 10. Conclusions  | 286 |

|------------------|-----|

| Acknowledgements | 287 |

| References       | 287 |

|                  |     |

|                  |     |

| Author Index     | 297 |

| Author Index     |     |

This page intentionally left blank

## Contributors

**Will Bamford** graduated from Lancaster University in 2005 with a BSc in IT and Media Communications. Currently in his second year of a PhD at Lancaster University performing research into novel mobile applications, with a focus on harnessing new mobile technologies such as GPS, RFID, Bluetooth and other mobile sensors such as 3D accelerometers and combining these with emerging web technologies and services to create new social/gaming experiences for mobile devices.

**Kirk W. Cameron** is an associate professor in the Department of Computer Science and director of the Scalable Performance (SCAPE) Laboratory at Virginia Polytechnic Institute and State University. His research interests include high-performance and grid computing, parallel and distributed systems, computer architecture, poweraware systems, and performance evaluation and prediction. Cameron received a PhD in computer science from Louisiana State University. He is a member of the IEEE and the IEEE Computer Society. Contact him at cameron@vt.edu.

**Fadi Chehimi** is an experienced Symbian programmer working for Mobica Ltd and studying part-time for a PhD at Lancaster University. His research interests are based around novel tools and methodologies for 3-D graphics, imaging and interactive mobile advertising on mobile phones.

**Paul Coulton** is a Senior Lecturer in Mobile Applications and was one of fifty mobile developers worldwide, selected from a community of two million, to be a Forum Nokia Champion. He has been a pioneer of mobile games particularly those incorporating novel interfaces and location based information and continues to drive innovation in the sector. Paul is a regular speaker at international conferences, including the Mobile GDC, and is highly respected both in the industrial and academic communities.

**Reuben Edwards** is Lecturer in games and m-commerce and has been at the forefront of innovative multimedia application development for over ten years. He is

#### CONTRIBUTORS

renowned for his extensive knowledge of development environments across all platforms and has also pioneered the use of many platforms in technology education and produced many cutting edge courses.

**Xizhou Feng** is a Research Associate in the Department of Computer Science at Virginia Polytechnic Institute and State University. His research interests include bioinformatics, computational biology, distributed system, high performance computing, and parallel algorithms. He received a PhD in Computer Science and Engineering from the University of South Carolina, and MS degree in Engineering Thermophysics from Tsinghua University, China. He is a member of the IEEE and the IEEE Computer Society. Contact him at fengx@cs.vt.edu.

**Rong Ge** is a PhD candidate in the Department of Computer Science and a researcher at the SCAPE Laboratory at Virginia Tech. Her research interests include performance modeling and analysis, parallel and distributed systems, power-aware systems, high-performance computing, and computational science. Ge received the BS degree and MS degree in Fluid Mechanics from Tsinghua University, China, and the MS degree in computer science from the University of South Carolina. She is a member of the IEEE, ACM and Upsilon Pi Epsilon. Contact her at ge@cs.vt.edu.

**Paul Gilbertson** is currently studying for his PhD at the Department of Communication Systems at Lancaster University in the UK. He has worked with Windows systems of all sizes, from Active Directory networks, to Windows Mobile phones and PDAs both as a programmer and whilst at APT in London. Paul is currently developing location aware software using .NET, Java, and Symbian OS technologies as part of his PhD.

**Rakesh Kumar** is an Assistant Professor in the Department of Electrical and Computer Engineering at the University of Illinois, Urbana-Champaign. His research interests include multicore and multithreaded architectures, low-power architectures, and on-chip interconnects. Kumar received a PhD in computer engineering from the University of California at San Diego, and a BS in computer science and engineering from the Indian Institute of Technology, Kharagpur. He is a member of the ACM. Contact him at rakeshk@uiuc.edu.

**Omer Rashid** is a PhD student at Lancaster University with over 3 years experience in research and mobile application development with Java. His research mainly focuses on novel networked mobile entertainment applications and his work has gained accreditation from Nokia and recently ACM. He is also a member of Mobile Radicals research initiative and the IEEE.

#### CONTRIBUTORS

**Walt Scacchi** received a PhD in Information and Computer Science at the University of California, Irvine in 1981. From 1981 until 1998, he was on the faculty at the University of Southern California. In 1999, he joined the Institute for Software Research at UC Irvine, and in 2002 became associate director for research at the Computer Game Culture and Technology Laboratory (http://www.ucgamelab.net). His research interests include open source software development, networked and grid-based computer games, knowledge-based systems for modeling and simulating complex engineering and business processes, developing decentralized heterogeneous information systems, and electronic commerce/business. Dr. Scacchi is a member of ACM, IEEE, AAAI, and the Software Process Association (SPA). He is an active researcher with more than 150 research publications and has directed 45 externally funded research projects. He also has had numerous consulting and visiting scientist positions with a variety of firms and research laboratories. In 2007, he serves as General Chair of the 3rd IFIP International Conference on Open Source Systems, Limerick, IE.

**Dean Tullsen** is a Professor in the Computer Science and Engineering Department at the University of California, San Diego. He received his PhD from the University of Washington in 1996, where his dissertation was *Simultaneous Multithreading*. He received his BS and MS degrees in Computer Engineering from UCLA. He was a computer architect for AT&T Bell Labs, and taught Computer Science for a year at a University in China prior to returning for his PhD. His research interests include the architecture of multithreading processors of all types (including simultaneous multithreading, multi-core, or the gray area in between), compiling for such architectures, and high performance architectures in general.

Wei Zhang received the BS degree in computer science from the Peking University in China in 1997, the MS from the Institute of Software, Chinese Academy of Sciences in 2000, and the PhD degree in computer science and engineering from the Pennsylvania State University in 2003. He is an assistant professor in the Electrical and Computer Engineering Department at Southern Illinois University Carbondale. His current research interests are in embedded systems, low-power computing, computer architecture and compiler. His research has been supported by NSF, Altera and SIUC. He is a member of the IEEE and ACM. He has served as a member of the technical program committees for several IEEE/ACM conferences and workshops. This page intentionally left blank

## Preface

In volume 69 of the **Advances in Computers** we present five chapters that discuss significant changes to both the hardware and software of present day computers. These chapters in the ever-changing landscape of information technology address how computers are evolving to address our differing needs for information technology as the computer becomes more ubiquitous in our everyday life. This series began back in 1960 and annually we present three volumes that offer approximately 18 chapters that describe the latest technology in the use of computers today.

The first chapter, "The Architecture of Efficient Multi-Core Processors: A Holistic Approach" by Rakesh Kumar and Dean M. Tullsen discusses the recent development of multicore processors. Moore's Law, essentially the doubling of computer power every 18 months, while not a natural law of the universe, has been amazingly true for over 30 years. However, as processor speeds have been increasing to clock rates of over 3 GHz ( $10^9$  cycles per second), it is not clear how much faster current technology can push processors. One way to increase this power is to put multiple processors on the same chip, thus using each clock cycle to run an instruction in each separate "core," and hence double processing power. Kumar and Tullsen discuss how efficient multicore processors can be developed.

Chapter 2, "Designing Computational Clusters for Performance and Power" by Kirk W. Cameron, Rong Ge and Xizhou Feng, continues with the development of high-performance processors discussed in Chapter 1. An important attribute, not often cited when discussing newer high-speed computers, is the generation of heat. As machines get faster and their clock rates increase, they generate more heat, thus requiring more powerful cooling devices like fans to get rid of this heat. This also means it takes more energy (and hence cost) to run these computers. In this chapter the authors discuss an architectural process that considers both maximal performance as well as minimizing power requirements in order to improve on the development of high speed processors.

In Chapter 3, "Compiler-Assisted Leakage Energy Reduction for Cache Memories," Wei Zhang considers the same heat problem discussed in Chapter 2, but addresses the issue of cache memories. Since processor speeds (on the order of  $10^9$  cycles per second) is much faster than the speeds of accessing memory (on the order

#### PREFACE

of  $10^8$  cycles per second), one way to increase processor performance is to keep a copy of part of main memory in the processor as a high-speed *cache* memory. This cache memory has the same heat generation problem discussed in the previous chapter. Dr. Wei discusses mechanisms to minimize energy (i.e., heat) losses in these memories by using compilation techniques to control cache accesses.

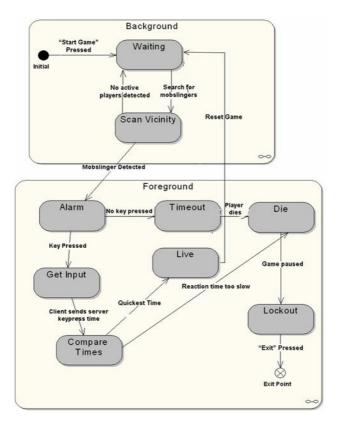

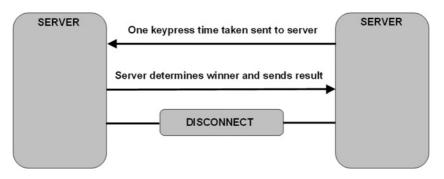

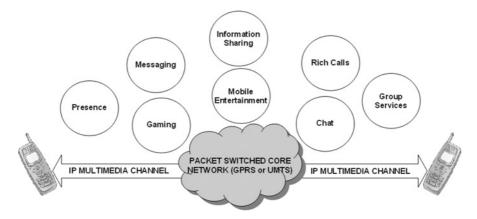

In "Mobile Games: Challenges and Opportunities" (Chapter 4) by Paul Coulton, Will Bamford, Fadi Chehimi, Reuben Edwards, Paul Gilbertson, and Omer Rashid, the authors discuss a new computer technology that is probably the fastest growing market—that of mobile phones. Phones have grown far beyond the simple concept of making a telephone call when not tethered by a wire to a land-based telephone network. Phones are powerful miniature computers with tiny console screens and only a few keys (the digits plus a few others) rather than a full desktop computer keyboard. Users often have the desire to play a game while waiting for other events to happen. So the design problem for mobile games is quite different from the established video game industry. You need a game that works on a small screen, only has a few keys for input, and can be played in short bursts of time. This chapter discusses these design constraints and future directions for this growing industry.

In the final chapter of this volume, "Free/Open Source Software Development: Recent Research Results and Methods" (Chapter 5), Walt Scacchi discusses open source development. Rather than have software developed and sold by a company, a group of individuals organize to develop and give away the software for free. The basic question is "Why?". In this chapter, the author discusses the sociology of how such groups form, why they do it, and how companies still make a profit on this form of development. *Open Source* is probably the most significant change in building some complex systems over the past 10 years, and it promises to have a profound effect on new software development in the future.

I hope that you find these chapters to be of value to you. I am always looking for new topics to explore. If we have not covered a relevant topic for several years, or if you wish to contribute a topic you believe you are an expert on, please let me know. I can be reached at mvz@cs.umd.edu.

> Marvin Zelkowitz University of Maryland and Fraunhofer Center, Maryland College Park, Maryland

## The Architecture of Efficient Multi-Core Processors: A Holistic Approach

## RAKESH KUMAR

Coordinated Science Laboratory University of Illinois at Urbana-Champaign Urbana, IL 61801 USA rakeshk@uiuc.edu

## DEAN M. TULLSEN

Department of Computer Science and Engineering University of California, San Diego La Jolla, CA 92093-0404 USA tullsen@cs.ucsd.edu

#### Abstract

The most straightforward methodology for designing a multi-core architecture is to replicate an off-the-shelf core design multiple times, and then connect the cores together using an interconnect mechanism. However, this methodology is "multi-core oblivious" as subsystems are designed/optimized unaware of the overall chip-multiprocessing system they would become parts of. The chapter demonstrates that this methodology is inefficient in terms of area/power. It recommends a holistic approach where the subsystems are designed from the ground up to be effective components of a complete system.

The inefficiency in "multi-core oblivious" designs comes from many sources. Having multiple replicated cores results in an inability to adapt to the demands of execution workloads, and results in either underutilization or overutilization of processor resources. *Single-ISA (instruction-set architecture) heterogeneous multi-core architectures* host cores of varying power/performance characteristics on the die, but all cores are capable of running the same ISA. Such a processor can result in significant power savings and performance improvements if the applications are mapped to cores judiciously. The paper also presents holistic design methodologies for such architectures. Another source of inefficiency is blind replication of over-provisioned hardware structures. *Conjoined-core chip multiprocessing* allows adjacent cores of a multi-core architecture to share some resources. This can result in significant area savings with little performance degradation. Yet another source of inefficiency is the interconnect. The interconnection overheads can be very significant for a "multi-core oblivious" multi-core design—especially as the number of cores increases and the pipelines get deeper. The paper demonstrates the need to co-design the cores, the memory and the interconnection to address the inefficiency problem, and also makes several suggestions regarding co-design.

| 1. | Introduction                                                     | 3  |

|----|------------------------------------------------------------------|----|

|    | 1.1. A Naive Design Methodology for Multi-Core Processors        | 3  |

|    | 1.2. A Holistic Approach to Multi-Core Design                    | 4  |

| 2. | The Move to Multi-Core Processors                                | 5  |

|    | 2.1. Early Multi-Core Efforts                                    | 7  |

| 3. | Holistic Design for Adaptability: Heterogeneous Architectures    | 9  |

|    | 3.1. Workload Diversity                                          | 10 |

|    | 3.2. Single-ISA Heterogeneous Multi-Core Architectures           | 10 |

|    | 3.3. Power Advantages of Architectural Heterogeneity             | 19 |

|    | 3.4. Overview of Other Related Proposals                         | 31 |

|    | 3.5. Designing Multi-Cores from the Ground Up                    | 32 |

| 4. | Amortizing Overprovisioning through Conjoined Core Architectures | 45 |

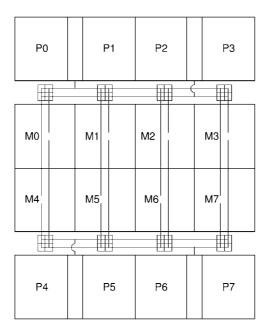

|    | 4.1. Baseline Architecture                                       | 46 |

|    | 4.2. Conjoined-Core Architectures                                | 47 |

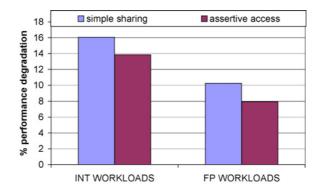

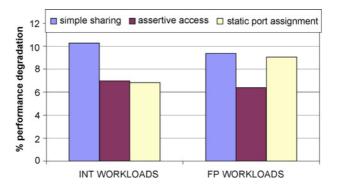

|    | 4.3. Simple Sharing                                              | 53 |

|    | 4.4. Intelligent Sharing of Resources                            | 58 |

|    | 4.5. A Unified Conjoined-Core Architecture                       | 61 |

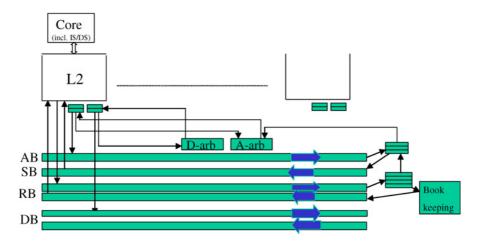

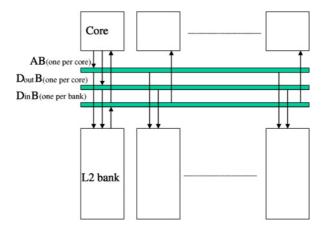

| 5. | Holistic Design of the Multi-Core Interconnect                   | 62 |

|    | 5.1. Interconnection Mechanisms                                  | 62 |

|    | 5.2. Shared Bus Fabric                                           | 62 |

|    | 5.3. P2P Links                                                   | 65 |

|    | 5.4. Crossbar Interconnection System                             | 66 |

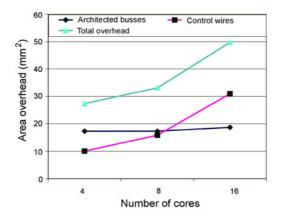

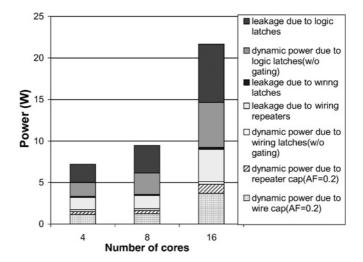

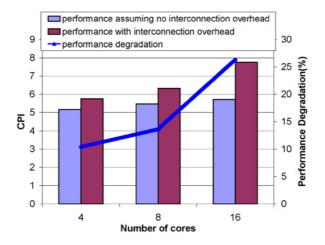

|    | 5.5. Modeling Interconnect Area, Power, and Latency              | 67 |

|    | 5.6. Modeling the Cores                                          | 69 |

|    | 5.7. Shared Bus Fabric: Overheads and Design Issues              | 71 |

|    | 5.8. Shared Caches and the Crossbar                              | 76 |

|    | 5.9. An Example Holistic Approach to Interconnection             | 79 |

| 6. | Summary and Conclusions                                          | 81 |

|    | Acknowledgements                                                 | 82 |

|    | References                                                       | 82 |

2

## 1. Introduction

The microprocessor industry has seen a tremendous performance growth since its inception. The performance of processors has increased by over 5000 times since the time Intel introduced the first general-purpose microprocessor [8]. This increase in processor performance has been fueled by several technology shifts at various levels of the processor design flow—architecture, tools and techniques, circuits, processes, and materials. Each of these technology shifts not only provide a jump in performance, but also require us to rethink the basic assumptions and processes that govern how we architect systems.

Specifically, at the architectural level, we have moved from scalar processing, where a processor executes one instruction every clock cycle, to superscalar processing, to out-of-order instruction execution, to on-chip hardware multithreading (e.g., simultaneous multithreading). We are now at the cusp of another major technology shift at the architectural level. This technology shift is the introduction of multi-core architectures—i.e., architectures with multiple processing nodes on the same die. Such processors, also called chip multiprocessors (CMPs), not only support multiple streams of program execution at the same time, but provide productivity advantages over monolithic processors due to the relative simplicity of the cores and the shorter design cycles for the processor core. Such processors can also make better use of the hardware resources, as the marginal utility of transistors is higher for a smaller processing node with a smaller number of transistors.

But like many other technological shifts, we must also change the way we design these architectures to take full advantage of the new technology. How, then, do we approach the design of such an architecture? What traditional architectural assumptions no longer apply? How do we design the components of such a system so that the whole processor meets our design goals?

This chapter seeks to address these questions.

## 1.1 A Naive Design Methodology for Multi-Core Processors

One suggested (as well as practiced) methodology for multi-core design is to take an off-the-shelf core design, perhaps optimize it for power and/or performance, replicate it multiple times, and then connect the cores together using a good interconnection mechanism in a way that maximizes performance for a given area and/or power budget. This is a clean, relatively easy way to design a multi-core processor because one design team can work on the core, another can work on the caches, the third can work on the interconnect, and then there can be a team of chip integrators who will put them all together to create a multi-core processor. Such a methodology encourages modularity as well as reuse, and serves to keep the design costs manageable.

However, this methodology is "multi-core oblivious." This is because each subsystem that constitutes the final chip multiprocessing system is designed and optimized without any cognizance of the overall system it would become a part of. For example, a methodology like the above forces each subsystem to target the entire universe of applications (i.e., a set of all possible applications that a processor is expected to run).

This chapter shows that "multi-core oblivious" designs result in inefficient processors in terms of area and power. This is because the above constraint results in either overutilization or underutilization of processor resources. For example, Pentium Extreme is a dual-core Intel processor that is constructed by replicating two identical off-the-shelf cores. While the area and power cost of duplicating cores is 2X (in fact, even more considering the glue logic required), the performance benefits are significantly lower [66]. That paper shows that while the costs are superlinear with the number of cores for all "multi-core oblivious" designs, the benefits tend to be highly sublinear.

## 1.2 A Holistic Approach to Multi-Core Design

In the era of uniprocessor microprocessors, each CPU core was expected to provide high general-purpose performance (that is, provide high performance for a wide range of application characteristics), high energy efficiency, reliability, and high availability. In a multi-core processor, the user will have the same expectations, but they will be applied to the entire processor. In this architecture, then, no single component (e.g., processor cores, caches, interconnect components) need meet any of those constraints, as long as the whole system (the processor) meets those constraints. This presents a degree of freedom not previously available to architects of mainstream high-performance processors.

The multi-core oblivious approach, for example, would build a system out of reliable processor cores. The holistic approach designs each core to be part of a reliable system. The difference between these two approaches is significant. The implications are actually relatively well understood in the realm of reliability. We can build a reliable and highly available multi-core system, even if the individual cores are neither. However, the implications of a holistic approach to delivering high general-purpose performance and energy efficiency have not been explored, and that is the focus of this chapter. As an example of our holistic approach to processor design, we show that a processor composed of general-purpose cores does not deliver the same average general-purpose performance as a processor composed of specialized cores, none optimized to run every program well. Section 3 discusses how "multi-core oblivious" designs fail to adapt to workload diversity. It presents *single-ISA heterogeneous multi-core architectures* as a holistic solution to adapting to diversity. These architectures can provide significantly higher throughput for a given area or power budget. They can also be used to reduce processor power dissipation. That section also discusses methodologies for holistic, ground-up design of multi-core architecture and demonstrates their benefits over processors designed using off-the-shelf components.

Section 4 introduces overprovisioning as another source of inefficiency in multicore architectures that are designed by blindly replicating cores. Such architectures unnecessarily multiply the cost of overprovisioning by the number of compute nodes. *Conjoined-core chip-multiprocessing* is a holistic approach to addressing overprovisioning. Conjoined-core multi-core processors have adjacent cores sharing large, overprovisioned structures. Intelligently scheduling accesses to the shared resources enables conjoined-core architectures to achieve significantly higher efficiency (*throughput/area*) than their "multi-core oblivious" counterparts.

Section 5 details the overheads that conventional interconnection mechanisms entail, especially as the number of cores increases and as transistors get faster. It shows that overheads become unmanageable very soon and require a holistic approach to designing multi-cores where the interconnect is co-designed with the cores and the caches. A high-bandwidth interconnect, for example, can actually decrease performance if it takes resources needed for cores and caches. Several examples are presented for the need to co-design.

#### 2. The Move to Multi-Core Processors

This section provides background information on multi-core architectures and explains why we are seeing the entire industry now move in this architectural direction. We also provide an overview of some groundbreaking multi-core efforts.

The processor industry has made giant strides in terms of speed and performance. The first microprocessor, the Intel 4004 [8], ran at 784 KHz while the microprocessors of today run easily in the GHz range due to significantly smaller and faster transistors. The increase in performance has been historically consistent with Moore's law [70] that states that the number of transistors on the processor die doubles every eighteen months due to shrinking of the transistors every successive process technology.

However, the price that one pays for an increment in performance has been going up rapidly as well. For example, as Horowitz et al. [47] show, the power cost for squeezing a given amount of performance has been going up linearly with the performance of the processor. This represents, then, a super-exponential increase in power over time (performance has increased exponentially, power/performance increases linearly, and total power is the product of those terms). Similarly, the area cost for squeezing a given amount of performance has been going up as well.

An alternative way to describe the same phenomenon is that the marginal utility of each transistor we add to a processor core is decreasing. While area and power are roughly linear with the number of transistors, performance is highly sublinear with the number of transistors. Empirically, it has been close to the square root of the number of transistors [46,45]. The main reason why we are on the wrong side of the square law is that we have already extracted the easy ILP (instruction-level parallelism) through techniques like pipelining, superscalar processing, out-of-order processing, etc. The ILP that is left is difficult to extract. However, technology keeps making transistors available to us at the rate predicted by Moore's Law (though it has slowed down, of late). We have reached a point where we have more transistors available than we know how to make effective use of in a conventional monolithic processor environment.

Multi-core computing, however, allows us to cheat the square law. Instead of using all the transistors to construct a monolithic processor targeting high single-thread performance, we can use the transistors to construct multiple simpler cores where each core can execute a program (or a thread of execution). Such cores can collectively provide higher many-thread performance (or throughput) than the baseline monolithic processor at the expense of single-thread performance.

Consider, for example, the Alpha 21164 and Alpha 21264 cores. Alpha 21164 (also called, and henceforth referred to as, EV5) is an in-order processor that was originally implemented in 0.5 micron technology [17]. Alpha 21264 (also called, and henceforth referred to as, EV6) is an out-of-order processor that was originally implemented in 0.35 micron technology [18]. If we assume both the processors to be mapped to the same technology, an EV6 core would be roughly five times bigger than an EV5 core. If one were to take a monolithic processor like EV6, and replace it with EV5 cores, one could construct a multi-core that can support five streams of execution for the same area budget (ignoring the cost of interconnection and glue logic). However, for the same technology, the single-thread performance of an EV6 core is only roughly 2.0-2.2 times that of an EV5 core (assuming performance is proportional to the square root of the number of transistors). Thus, if we replaced an EV6 monolithic processor by a processor with five EV5 cores, the aggregate throughput would be more than a factor of two higher than the monolithic design for the same area budget. Similar throughput gains can be shown even for a fixed power budget. This potential to get significantly higher aggregate performance for the same budget is the main motivation for multi-core architectures.

Another advantage of multi-core architectures over monolithic designs is improved design productivity. The more complex the core, the higher the design and verification costs in terms of time, opportunity, and money. Several recent monolithic designs have taken several thousand man years worth of work. A multi-core approach enables deployment of pre-existing cores, thereby bringing down the design and verification costs. Even when the cores are designed from scratch, the simplicity of the cores can keep the costs low. With increasing market competition and declining hardware profit margins, the time-to-market of processors is more important than before, and multi-cores should improve that metric.

## 2.1 Early Multi-Core Efforts

This section provides an overview of some of the visible general-purpose multicore projects that have been undertaken in academia and industry. It does not describe all multi-core designs, but is biased towards the first few general-purpose multi-core processors that broke ground for mainstream multi-core computing.

The first multi-core description was the Hydra [43,44], first described in 1994. Hydra was a 4-way chip multiprocessor that integrated four 250 MHz MIPS cores on the same die. The cores each had 8 KB private instruction and data caches and shared a 128 KB level-2 cache. Hydra was focused not only on providing hardware parallelism for throughput-oriented applications, but also on providing high single-thread performance for applications that can be parallelized into threads by a compiler. A significant amount of support was also provided in the hardware to enable threadlevel speculation efforts. Hydra was never implemented, but an implementation of Hydra (0.25 micron technology) was estimated to take up 88 mm<sup>2</sup> of area.

One of the earliest commercial multi-core proposals, Piranha [23] (description published in 2000) was an 8-way chip multiprocessor designed at DEC/Compaq WRL. It was targeted at commercial, throughput-oriented workloads whose performance is not limited by instruction-level parallelism. It integrated eight simple, in-order processor cores on the die. Each core contained private 64 KB instruction and data caches and shared a 1 MB L2 cache. The processor also integrated on the chip functionality required to support scalability of the processor to large multiprocessing systems. Piranha also was never implemented.

Around the same time as Piranha, Sun started the design of the MAJC 5200 [86]. It was a two-way chip multiprocessor where each core was a four-issue VLIW (very large instruction word) processor. The processor was targeted at multimedia and Java applications. Each core had a private 16 KB L1 instruction cache. The cores shared a 16 KB dual-ported data cache. Small L1 caches and the lack of an on-chip L2 cache made the processor unsuitable for many commercial workloads. One implementation of MAJC 5200 (0.22 micron technology) took 15 W of power and 220 mm<sup>2</sup> of area. Sun also later came out with other multi-core products, like UltraSparc-IV [83] and Niagara [55].

IBM's multi-core efforts started with Power4 [49]. Power4, a contemporary of MAJC 5200 and Piranha, was a dual-core processor running at 1 GHz where each core was a five-issue out-of-order superscalar processor. Each core consisted of a private direct-mapped 32 KB instruction cache and a private 2-way 32 KB data cache. The cores were connected to a shared triply-banked 8-way set-associative L2 cache. The connection was through a high-bandwidth crossbar switch (called crossbar-interface unit). Four Power4 chips could be connected together within a multi-chip module and made to logically share the L2. One implementation of Power4 (in 0.13 micron technology) consisted of 184 million transistors and took up 267 mm<sup>2</sup> in die-area.

IBM also later came up with successors to Power4, like Power5 [50] and Power6. However, IBM's most ambitious multi-core offering arguably has been Cell [52]. Cell is a multi-ISA heterogeneous chip multiprocessor that consists of one two-way simultaneous multithreading (SMT) [90,89] dual-issue Power core and eight dualissue SIMD (single instruction, multiple data) style Synergistic Processing Element (SPE) cores on the same die. While the Power core executes the PowerPC instruction set (while supporting the vector SIMD instruction set at the same time), the SPEs execute a variable width SIMD instruction set architecture (ISA). The Power core has a multi-level storage hierarchy—32 KB instruction and data caches, and a 512 KB L2. Unlike the Power core, the SPEs operate only on their local memory (local store, or LS). Code and data must be transferred into the associated LS for an SPE to operate on. LS addresses have an alias in the Power core address map, and transfers between an individual LS and the global memory are done through DMAs (direct memory accesses). An implementation of Cell in 90 nm operates at 3.2 GHz, consists of 234 million transistors and takes 229 mm<sup>2</sup> of die area.

The first x86 multi-core processors were introduced by AMD in 2005. At the time of writing this chapter, AMD offers Opteron [2], Athlon [3], and Turion [1] dual-core processors serving different market segments. Intel's dual-core offerings include Pentium D [10], Pentium Extreme [11], Xeon [12], and Core Duo [9] processors. The approach Intel has taken so far is to take last-generation, aggressive designs and put two on a die when space allows, rather than to target less aggressive cores. The Pentium Processor Extreme includes designs that are both dual-core and hardware multithreaded on each core.

One constraint for all the above multi-core designs was that they had to be capable of running legacy code in their respective ISAs. This restricted the degree of freedom in architecture and design of these processors. Three academic multi-core projects that were not bound by such constraints were RAW, TRIPS, and WaveScalar.

The RAW [91] processor consists of sixteen identical tiles spread across the die in a regular two-dimensional pattern. Each tile consists of communication routers, one scalar core, an FPU (floating-point unit), a 32 KB DCache, and a software-managed 96 KB ICache. Tiles are sized such that the latency of communication between two adjacent tiles is always one cycle. Tiles are connected using on-chip networks that interface with the tiles through the routers. Hardware resources on a RAW processor (tiles, pins, and the interconnect) are exposed to the ISA. This enables the compiler to generate aggressive code that maps more efficiently to the underlying computation substrate.

The TRIPS [76] processor consists of four large cores that are constructed out of small decentralized, polymorphous structures. The cores can be partitioned into small execution nodes when a program with high data-level parallelism needs to be executed. These execution nodes can also be logically chained when executing streaming programs. Like RAW, the microarchitecture is exposed to the ISA. Unlike RAW and other multi-cores discussed above, the unit of execution is a hyperblock. A hyperblock commits only when all instructions belonging to a hyperblock finish execution.

WaveScalar [84] attempts to move away from Von-Neumann processing in order to get the full advantage of parallel hardware. It has a dataflow instruction set architecture that allows for traditional memory ordering semantics. Each instruction executes on an ALU (arithmetic logic unit) that sits inside a cache, and explicitly forwards the result to the dependent instructions. The ALU + cache is arranged as regular tiles, thereby allowing the communication overheads to be exposed to hardware. Like RAW and TRIPS, wavescalar also supports all the traditional imperative languages.

There have been multi-core offerings in non-mainstream computing markets as well. A few examples are Broadcom SiByte (SB1250, SB1255, SB1455) [5], PA-RISC (PA-8800) [7], Raza Microelectronics' XLR processor [13] that has eight MIPS cores, Cavium Networks' Octeon [6] processor that has 16 MIPS cores, Arm's MPCore processor [4], and Microsoft's Xbox 360 game console [14] that uses a triple-core PowerPC microprocessor.

## 3. Holistic Design for Adaptability: Heterogeneous Architectures

The rest of this chapter discusses various holistic approaches to multi-core design. Each of these approaches results in processors that are significantly more efficient than their "multi-core oblivious" counterparts.

First, we discuss the implication of workload diversity on multi-core design and present a new class of holistically-designed architectures that deliver significant gains in efficiency. Section 3.1 discusses the diversity present in computer workloads and how naively-designed multi-core architectures do not adapt well. Section 3.2

introduces *single-ISA heterogeneous multi-core architectures* that can adapt to workload diversity. That section also discusses the scheduling policies and mechanisms that are required to effect adaptability. Section 3.3 discusses the power advantages of the architecture and the corresponding scheduling policies. Section 3.4 provides an overview of other work evaluating advantages of heterogeneous multi-core architectures. Section 3.5 discusses a holistic design methodology for such architectures.

## 3.1 Workload Diversity

The amount of diversity among applications that a typical computer is expected to run can be considerable. For example, there can often be more than a factor of ten difference in the average performance of SPEC2000 applications gcc and mcf [79]. Even in the server domain there can be diversity among threads. Here the diversity can be because of batch processing, different threads processing different inputs, or threads having different priorities. Even in such a homogeneous workload, if each thread experiences phased behavior, different phases will typically be active in different threads at the same time.

A multi-core oblivious design (i.e., a homogeneous design that consists of identical cores) can target only a single point efficiently in the diversity spectrum. For example, a decision might need to be made beforehand if the core should be designed to target *gcc* or *mcf*. In either case, an application whose resource demands are different from those provided by the core will suffer—the resource mismatch will either result in underutilization of the resulting processor or it will result in low program performance.

Similarly, there is diversity within applications [79], as different phases of the same application often have different execution resource needs. Note that this is the same problem that a general-purpose uniprocessor faces as well, as the same design is expected to perform well for the entire universe of applications. There is a new form of diversity, as well, that uniprocessor architectures did not need to account for. A general-purpose multi-core should also provide good performance whether there is one thread (program) running, eight threads running, or one hundred.

## 3.2 Single-ISA Heterogeneous Multi-Core Architectures

To address the poor adaptability of homogeneous multi-core architectures, we present single-ISA heterogeneous multi-core architectures. That is, architectures with multiple core types on the same die. The cores are all capable of executing the same ISA (instruction-set architecture), but represent different points in the power/performance continuum—for example, a low-power, low-performance core and a high-power, high-performance core on the same die.

The advantages of single-ISA heterogeneous architectures stem from two sources. The first advantage results from a more *efficient adaptation to application diversity*. Given a set of diverse applications and heterogeneous cores, we can assign applications (or phases of applications) to cores such that those that benefit the most from complex cores are assigned to them, while those that benefit little from complex cores are assigned to smaller, simpler cores. This allows us to approach the performance of an architecture with a larger number of complex cores.

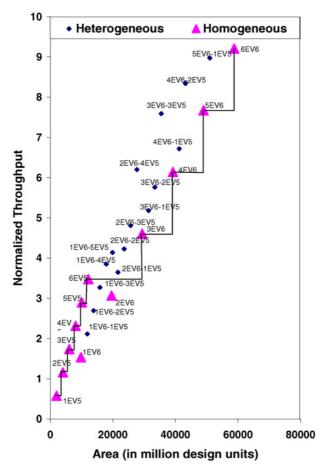

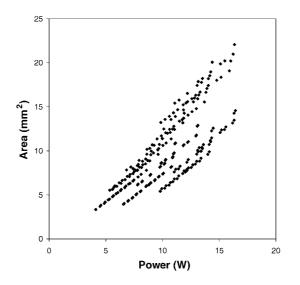

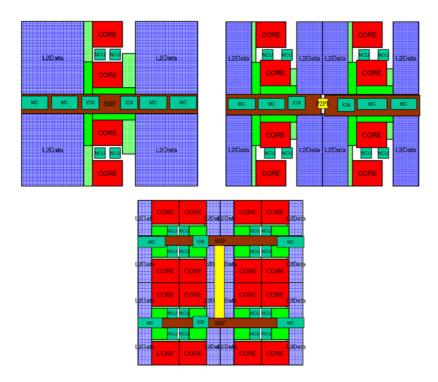

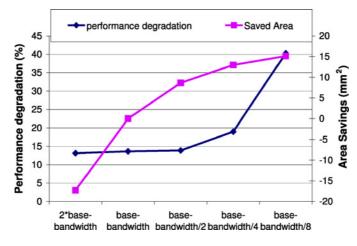

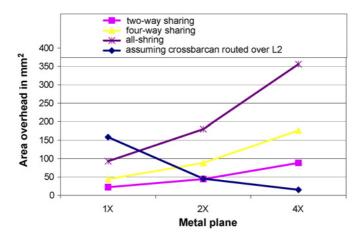

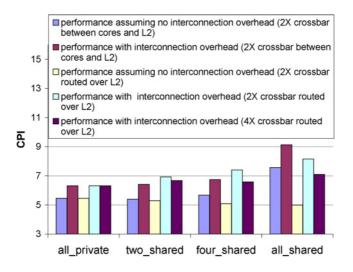

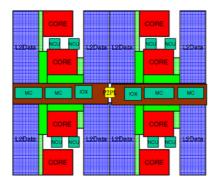

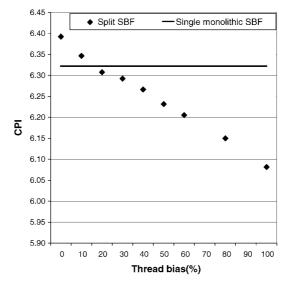

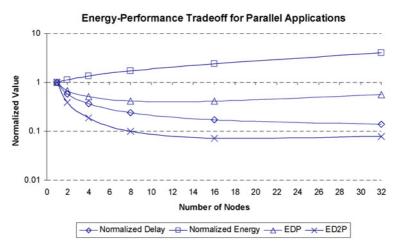

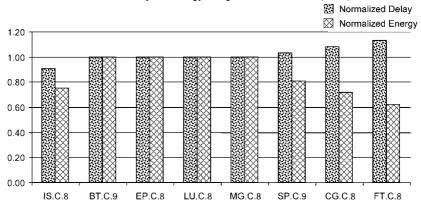

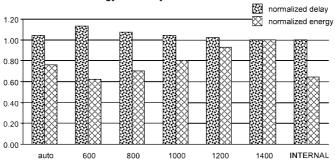

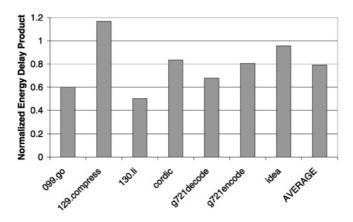

FIG. 1. Exploring the potential of heterogeneity: Comparing the throughput of six-core homogeneous and heterogeneous architectures for different area budgets.

The second advantage from heterogeneity results from a more *efficient use of die* area for a given thread-level parallelism. Successive generations of microprocessors have been providing diminishing performance returns per chip area [47] as the performance improvement of many microprocessor structures (e.g., cache memories) is less than linear with their size. Therefore, in an environment with large amounts of thread-level parallelism (TLP, the number of programs or threads currently available to run on the system), higher throughputs could be obtained by building a large number of small processors, rather than a small number of large processors. However, in practice the amount of thread level parallelism in most systems will vary with time. This implies that building chip-level multiprocessors with a mix of cores—some large cores with high single-thread performance and some small cores with high throughput per die area—is a potentially attractive approach.

To explore the potential from heterogeneity, we model a number of chip multiprocessing configurations that can be derived from combinations of two existing off-the-shelf processors from the Alpha architecture family—the EV5 (21164) and the EV6 (21264) processors. Figure 1 compares the various combinations in terms of their performance and their total chip area. In this figure, performance is that obtained from the best static mapping of applications constituting multiprogrammed SPEC2000 workloads to the processor cores. The solid staircase line represents the maximum throughput obtainable using a homogeneous configuration for a given area.

We see from this graph that over a large portion of the graph the highest performance architecture for a given area limit, often by a significant margin, is a heterogeneous configuration. The increased throughput is due to the increased number of contexts as well as improved processor utilization.

#### 3.2.1 Methodology to Evaluate Multi-Core Architectures

This section discusses the methodological details for evaluating the benefits of heterogeneous multi-core architectures over their homogeneous counterparts. It also details the hardware assumptions made for the evaluation and provides the methodology for constructing multiprogrammed workloads for evaluation. We also discuss the simulation details and the evaluation metrics.

**3.2.1.1** Supporting Multi-Programming. The primary issue when using heterogeneous cores for greater throughput is with the scheduling, or assignment, of jobs to particular cores. We assume a scheduler at the operating system level that has the ability to observe coarse-grain program behavior over particular intervals, and move jobs between cores. Since the phase lengths of applications are typically large [78], this enables the cost of core switching to be piggybacked with the operating system context-switch overhead. Core switching overheads are modeled in detail

for the evaluation of dynamic scheduling policies presented in this chapter—ones where jobs can move throughout execution.

**3.2.1.2** Hardware Assumptions. Table I summarizes the configurations used for the EV5 and the EV6 cores that we use for our throughput-related evaluations. The cores are assumed to be implemented in 0.10 micron technology and are clocked at 2.1 GHz.

In addition to the individual L1 caches, all the cores share an on-chip 4 MB, 4-way set-associative, 16-way L2 cache. The cache line size is 128 bytes. Each bank of the L2 cache has a memory controller and an associated RDRAM channel. The memory bus is assumed to be clocked at 533 MHz, with data being transferred on both edges of the clock for an effective frequency of 1 GHz and an effective bandwidth of 2 GB/s per bank. A fully-connected matrix crossbar interconnect is assumed between the cores and the L2 banks. All L2 banks can be accessed simultaneously, and bank conflicts are modeled. The access time is assumed to be 10 cycles. Memory latency was set to be 150 ns. We assume a snoopy bus-based MESI coherence protocol and model the writeback of dirty cache lines for every core switch.

Table I also presents the area occupied by the core. These were computed using a methodology outlined in Section 3.3. As can be seen from the table, a single EV6 core occupies as much area as 5 EV5 cores.

To evaluate the performance of heterogeneous architectures, we perform comparisons against homogeneous architectures occupying equivalent area. We assume that the total area available for cores is around 100 mm<sup>2</sup>. This area can accommodate a maximum of 4 EV6 cores or 20 EV5 cores. We expect that while a 4-EV6 homogeneous configuration would be suitable for low-TLP (thread-level parallelism) environments, the 20-EV5 configuration would be a better match for the cases where TLP is high. For studying heterogeneous architectures, we choose a configuration with 3 EV6 cores and 5 EV5 cores with the expectation that it would perform well

| CONTROURATION AND AREA OF THE EVE AND EVE CORES |           |                |  |  |  |  |  |  |

|-------------------------------------------------|-----------|----------------|--|--|--|--|--|--|

| Processor                                       | EV5       | EV6            |  |  |  |  |  |  |

| Issue-width                                     | 4         | 6 (000)        |  |  |  |  |  |  |

| I-Cache                                         | 8 KB, DM  | 64 KB, 2-way   |  |  |  |  |  |  |

| D-Cache                                         | 8 KB, DM  | 64 KB, 2-way   |  |  |  |  |  |  |

| Branch Pred.                                    | 2K-gshare | hybrid 2-level |  |  |  |  |  |  |

| Number of MSHRs                                 | 4         | 8              |  |  |  |  |  |  |

| Number of threads                               | 1         | 1              |  |  |  |  |  |  |

| Area (in mm <sup>2</sup> )                      | 5.06      | 24.5           |  |  |  |  |  |  |

TABLE I

CONFIGURATION AND AREA OF THE EV5 AND EV6 CORES

over a wide range of available thread-level parallelism. It would also occupy roughly the same area.

**3.2.1.3** Workload Construction. All our evaluations are done for various thread counts ranging from one through a maximum number of available processor contexts. Instead of choosing a large number of benchmarks and then evaluating each number of threads using workloads with completely unique composition, we instead choose a relatively small number of SPEC2000 [82] benchmarks (8) and then construct workloads using these benchmarks. These benchmarks are evenly distributed between integer benchmarks (*crafty, mcf, eon, bzip2*) and floating-point benchmarks (*applu, wupwise, art, ammp*). Also, half of them (*applu, bzip2, mcf, wupwise*) have a large memory footprint (over 175 MB), while the other half (*ammp, art, crafty, eon*) have memory footprints of less than 30 MB.

All the data points are generated by evaluating 8 workloads for each case and then averaging the results. The 8 workloads at each level of threading are generated by constructing subsets of the workload consistent with the methodology in [90,81].

**3.2.1.4** Simulation Approach. Benchmarks are simulated using SMT-SIM [87], a cycle-accurate execution-driven simulator that simulates an out-of-order, simultaneous multithreading processor [90]. SMTSIM executes unmodified, statically linked Alpha binaries. The simulator was modified to simulate the various multi-core architectures.

The Simpoint tool [78] was used to find good representative fast-forward distances for each benchmark (how far to advance the program before beginning measured simulation). Unless otherwise stated, all simulations involving *n* threads were done for  $500 \times n$  million instructions. All the benchmarks are simulated using the SPEC *ref* inputs.

**3.2.1.5 Evaluation Metrics.** In a study like this, IPC (number of total instructions committed per cycle) is not a reliable metric as it would inordinately bias all the heuristics (and policies) against inherently slow-running threads. Any policy that favors high-IPC threads boosts the reported IPC by increasing the contribution from the favored threads. But this does not necessarily represent an improvement. While the IPC over a particular measurement interval might be higher, in a real system the machine would eventually have to run a workload inordinately heavy in low-IPC threads, and the artificially-generated gains would disappear. Therefore, we use weighted speedup [81,88] for our evaluations. In this section, weighted speedup measures the arithmetic sum of the individual IPCs of the threads constituting a workload divided by their IPC on a baseline configuration when running alone. This

metric makes it difficult to produce artificial speedups by simply favoring high-IPC threads.

## 3.2.2 Scheduling for Throughput: Analysis and Results

In this section, we demonstrate the performance advantage of the heterogeneous multi-core architectures for multithreaded workloads and demonstrate job-to-core assignment mechanisms that allow the architecture to deliver on its promise. The first two subsections focus on the former, and the rest of the section demonstrates the further gains available from a good job assignment mechanism.

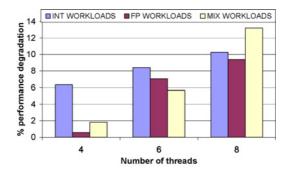

**3.2.2.1** Static Scheduling for Inter-thread Diversity. A heterogeneous architecture can exploit two dimensions of diversity in an application mix. The first is diversity between applications. The second is diversity over time within a single application. Prior work [78,92] has shown that both these dimensions of diversity occur in common workloads. In this section, we attempt to separate these two effects by first looking at the performance of a static assignment of applications to cores. Note that the static assignment approach may not eliminate the need for core switching in several cases, because the best assignment of jobs to cores will change as jobs enter and exit the system.

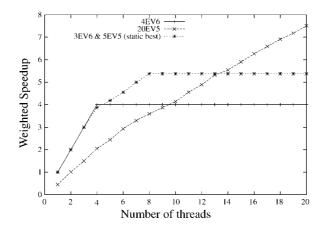

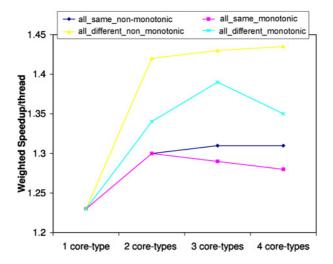

Figure 2 shows the results comparing one heterogeneous architecture against two homogeneous architectures all requiring approximately the same area. The heterogeneous architecture that we evaluate includes 3 EV6 cores and 5 EV5 cores, while the two homogeneous architectures that we study have 4 EV6 cores or 20 EV5 cores,

FIG. 2. Benefits from heterogeneity-static scheduling for inter-thread diversity.

respectively. For each architecture, the graph shows the average weighted speedup for varying number of threads.

For the homogeneous CMP configuration, we assume a straightforward scheduling policy, where as long as a core is available, any workload can be assigned to any core. For the heterogeneous case, we use an assignment that seeks to match the optimal static configuration as closely as possible. The optimal configuration would factor in both the effect of the performance difference between executing on a different core and the potential shared L2 cache interactions. However, determining this configuration is only possible by running all possible combinations. Instead, as a simplifying assumption, our scheduling policy assumes no knowledge of L2 interactions (only for determining core assignments-the interactions are still simulated) when determining the static assignment of workloads to cores. This simplification allows us to find the best configuration (defined as the one which maximizes weighted speedup) by simply running each job alone on each of our unique cores and using that to guide our core assignment. This results in consistently good, if not optimal, assignments. For a few cases, we compared this approach to an exhaustive exploration of all combinations; our results indicated that this results in performance close to the optimal assignment.

The use of weighted speedup as the metric ensures that those jobs assigned to the EV5 are those that are least affected (in relative IPC) by the difference between EV6 and EV5. In both the homogeneous and heterogeneous cases, once all the contexts of a processor get used, we just assume that the weighted speedup will level out as shown in Fig. 2. The effect when the number of jobs exceeds the number of cores in the system (e.g., additional context switching) is modeled more exactly in the following section.

As can be seen from Fig. 2, even with a simple static approach, the results show a strong advantage for heterogeneity over the homogeneous designs, for most levels of threading. The heterogeneous architecture attempts to combine the strengths of both the homogeneous configurations—CMPs of a few powerful processors (EV6 CMP) and CMPs of many less powerful processors (EV5 CMP). While for low threading levels, the applications can run on powerful EV6 cores resulting in high performance for each of the few threads, for higher threading levels, more applications can run on the added EV5 contexts enabled by heterogeneity, resulting in higher overall throughput.

The results in Fig. 2 show that the heterogeneous configuration achieves performance identical to the homogeneous EV6 CMP from 1 to 3 threads. At 4 threads, the optimum point for the EV6 CMP, that configuration shows a slight advantage over the heterogeneous case. However, this advantage is very small because with 4 threads, the heterogeneous configuration is nearly always able to find one thread that is impacted little by having to run on an EV5 instead of EV6. As soon as we have more than 4 threads, however, the heterogeneous processor shows clear advantage.

The superior performance of the heterogeneous architecture is directly attributable to the diversity of the workload mix. For example, *mcf* underutilizes the EV6 pipeline due to its poor memory behavior. On the other hand, benchmarks like *crafty* and *applu* have much higher EV6 utilization. Static scheduling on heterogeneous architectures enables the mapping of these benchmarks to the cores in such a way that overall processor utilization (average of individual core utilization values) is high.

The heterogeneous design remains superior to the EV5 CMP out to 13 threads, well beyond the point where the heterogeneous architecture runs out of processors and is forced to queue jobs. Beyond that, the raw throughput of the homogeneous design with 20 EV5 cores wins out. This is primarily because of the particular heterogeneous designs we chose. However, more extensive exploration of the design space than we show here confirms that we can always come up with a different configuration that is competitive with more threads (e.g., fewer EV6s, more EV5s), if that is the desired design point.

Compared to a homogeneous processor with 4 EV6 cores, the heterogeneous processor performs up to 37% better with an average 26% improvement over the configurations considering 1–20 threads. Relative to 20 EV5 cores, it performs up to 2.3 times better, and averages 23% better over that same range.

These results demonstrate that over a range of threading levels, a heterogeneous architecture can outperform comparable homogeneous architectures. Although the results are shown here only for a particular area and two core types, our experiments with other configurations (at different processor areas and core types) indicate that these results are representative of other heterogeneous configurations as well.

**3.2.2.2** Dynamic Scheduling for Intra-thread Diversity. The previous section demonstrated the performance advantages of the heterogeneous architecture when exploiting core diversity for inter-workload variation. However, that analysis has two weaknesses—it used unimplementable assignment policies in some cases (e.g., the static assignment oracle) and ignored variations in the resource demands of individual applications. This section solves each of these problems, and demonstrates the importance of good dynamic job assignment policies.

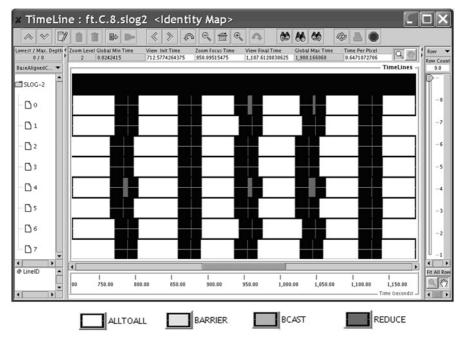

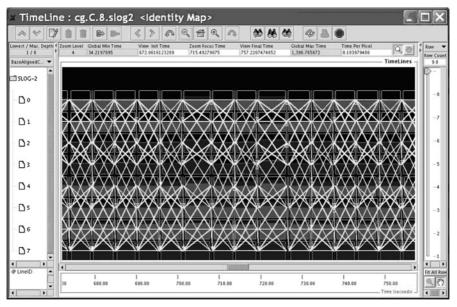

Prior work has shown that an application's demand for processor resources varies across phases of the application. Thus, the best match of applications to cores will change as those applications transition between phases. In this section, we examine implementable heuristics that dynamically adjust the mapping to improve performance. These heuristics are sampling-based. During the execution of a workload, every so often, a trigger is generated that initiates a *sampling phase*. In the *sampling* phase, the scheduler permutes the assignment of applications to cores. During this phase, the dynamic execution profiles of the applications being run are gathered by referencing hardware performance counters. These profiles are then used to create a new assignment, which is then employed during a much longer phase of execution, the *steady* phase. The steady phase continues until the next trigger. Note that applications continue to make forward progress during the sampling phase, albeit perhaps non-optimally.

In terms of the core sampling strategies, there are a large number of applicationto-core assignment permutations possible. We prune the number of permutations significantly by assuming that we would never run an application on a less powerful core when doing so would leave a more powerful core idle (for either the sampling phase or the steady phase). Thus, with four threads on our 3 EV6/5 EV5 configuration, four possible assignments are possible based on which thread gets allocated to the EV5. With more threads, the number of permutations increase, up to 56 potential choices with eight threads. Rather than evaluating all these possible alternatives, our heuristics only sample a subset of possible assignments. Each of these assignments are run for 2 million cycles. At the end of the sampling phase, we use the collected data to make assignments.

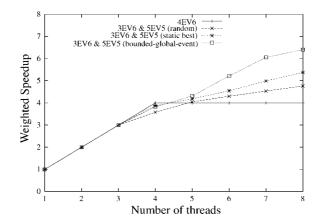

We experimented with several dynamic heuristics (more details on those heuristics can be found in [63]). Our best dynamic scheduling policy was what we call *bounded-global-event*. With this policy, we sum the absolute values of the percent changes in IPC for each application constituting a workload, and trigger a sampling phase when this value exceeds 100% (average 25% change for each of the four threads). The policy also initiates a sampling phase if more than 300 million cycles has elapsed since the last sampling phase, and avoids sampling if the global event trigger occurs within 50 million cycles since the last sampling phase. This strategy guards against oversampling and undersampling.

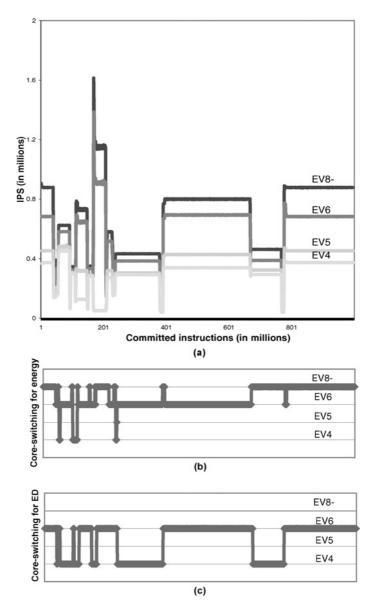

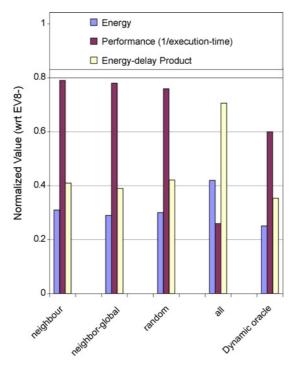

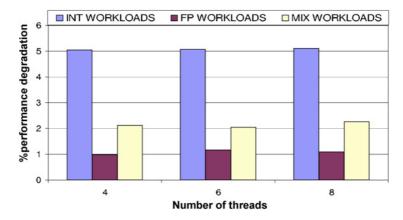

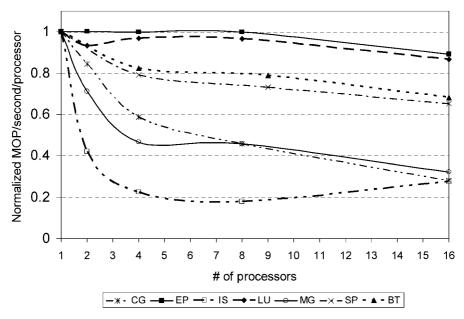

Figure 3 shows the results for the *bounded-global-event* dynamic scheduling heuristic comparing it against random scheduling as well as the best static mapping. The results presented in Fig. 3 indicate that dynamic heuristics which intelligently adapt the assignment of applications to cores can better leverage the diversity advantages of a heterogeneous architecture. Compared to the base homogeneous architecture, the best dynamic heuristic achieves close to a 63% improvement in throughput in the best case (for 8 threads) and an average improvement in throughput of 17% over configurations running 1–8 threads. Even more interesting, the best dynamic heuristic achieves a weighted speedup of 6.5 for eight threads, which is close to 80% of the optimal speedup (8) achievable for this configuration (despite the fact that over half of our cores have roughly half the raw computation power of the baseline

FIG. 3. Benefits of dynamic scheduling.

core!). In contrast, the homogeneous configuration achieves only 50% of the optimal speedup. The heterogeneous configuration, in fact, beats the homogeneous configuration with 20 EV5 cores till the number of threads exceeds thirteen. We have also demonstrated the importance of the intelligent dynamic assignment, which achieves up to 31% improvement over a baseline random scheduler.

#### 3.3 Power Advantages of Architectural Heterogeneity

The ability of *single-ISA heterogeneous multi-core architectures* to adapt to workload diversity can also be used for improving the power and energy efficiency of processors. The approach again relies on a chip-level multiprocessor with multiple, diverse processor cores. These cores all execute the same instruction set, but include significantly different resources and achieve different performance and energy efficiency on the same application. During an application's execution, the operating system software tries to match the application to the different cores, attempting to meet a defined objective function. For example, it may be trying to meet a particular performance requirement or goal, but doing so with maximum energy efficiency.

## 3.3.1 Discussion of Core Switching

There are many reasons, some discussed in previous sections, why the best core for execution may vary over time. The demands of executing code vary widely between applications; thus, the best core for one application will often not be the best for the next, given a particular objective function (assumed to be some combination of

energy and performance). In addition, the demands of a single application can also vary across phases of the program.

Even the objective function can change over time, as the processor changes power conditions (e.g., plugged vs. unplugged, full battery vs. low battery, thermal emergencies), as applications switch (e.g., low priority vs. high priority job), or even within an application (e.g., a real-time application is behind or ahead of schedule).

The experiments in this section explore only a subset of these possible changing conditions. Specifically, we examine adaptation to phase changes in single applications. However, by simulating multiple applications and several objective functions, it also indirectly examines the potential to adapt to changing applications and objective functions. We believe a real system would see far greater opportunities to switch cores to adapt to changing execution and environmental conditions than the narrow set of experiments exhibited here.

## 3.3.2 Choice of Cores

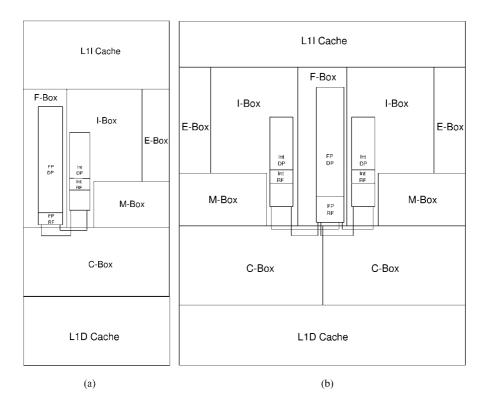

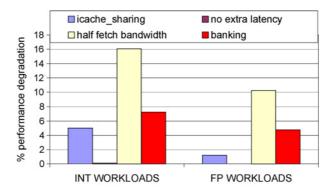

In this study, we consider a design that takes a series of previously implemented processor cores with slight changes to their interface—this choice reflects one of the key advantages of the CMP architecture, namely the effective amortization of design and verification effort. We include four Alpha cores—EV4 (Alpha 21064), EV5 (Alpha 21164), EV6 (Alpha 21264) and a single-threaded version of the EV8 (Alpha 21464), referred to as EV8-. These cores demonstrate strict gradation in terms of complexity and are capable of sharing a single executable. We assume the four

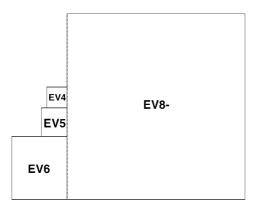

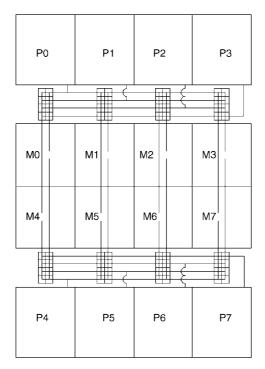

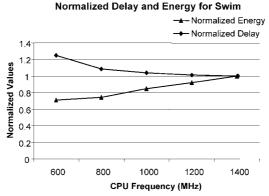

FIG. 4. Relative sizes of the Alpha cores when implemented in 0.10 micron technology.

cores have private L1 data and instruction caches and share a common L2 cache, phase-lock loop circuitry, and pins.

We chose the cores of these off-the-shelf processors due to the availability of real power and area data for these processors, except for the EV8 where we use projected numbers [30,35,54,69]. All these processors have 64-bit architectures. Note that technology mapping across a few generations has been shown to be feasible [57].

Figure 4 shows the relative sizes of the cores used in the study, assuming they are all implemented in a 0.10 micron technology (the methodology to obtain this figure is described in the next section). It can be seen that the resulting core is only modestly (within 15%) larger than the EV8- core by itself.

#### 3.3.3 Switching Applications between Cores

There is a cost to switching cores, so we must restrict the granularity of switching. One method for doing this would switch only at operating system timeslice intervals, when execution is in the operating system, with user state already saved to memory. If the OS decides a switch is in order, it powers up the new core, triggers a cache flush to save all dirty cache data to the shared L2, and signals the new core to start at a predefined OS entry point. The new core would then power down the old core and return from the timer interrupt handler. The user state saved by the old core would be loaded from memory into the new core at that time, as a normal consequence of returning from the operating system. Alternatively, we could switch to different cores at the granularity of the entire application, possibly chosen statically. In this study, we consider both these options.

In this work, we assume that unused cores are completely powered down, rather than left idle. Thus, unused cores suffer no static leakage or dynamic switching power. This does, however, introduce a latency for powering a new core up. We estimate that a given processor core can be powered up in approximately one thousand cycles of the 2.1 GHz clock. This assumption is based on the observation that when we power down a processor core we do not power down the phase-lock loop that generates the clock for the core. Rather, in our multi-core architecture, the same phase-lock loop generates the clocks for all cores. Consequently, the power-up time of a core is determined by the time required for the power buses to charge and stabilize. In addition, to avoid injecting excessive noise on the power bus bars of the multi-core processor, we assume a staged power up would be used.

In addition, our experiments confirm that switching cores at operating-system timer intervals ensures that the switching overhead has almost no impact on performance, even with the most pessimistic assumptions about power-up time, software overhead, and cache cold start effects. However, these overheads are still modeled in our experiments.

#### 3.3.4 Modeling Power, Area, and Performance

This section discusses the various methodological challenges of this study, including modeling the power, the real estate, and the performance of the heterogeneous multi-core architecture.

**3.3.4.1** Modeling of CPU Cores. The cores we simulate are roughly modeled after cores of EV4 (Alpha 21064), EV5 (Alpha 21164), EV6 (Alpha 21264) and EV8-. EV8- is a hypothetical single-threaded version of EV8 (Alpha 21464). The data on the resources for EV8 was based on predictions made by Joel Emer [35] and Artur Klauser [54], conversations with people from the Alpha design team, and other reported data [30,69]. The data on the resources of the other cores are based on published literature on these processors [16–18].

The multi-core processor is assumed to be implemented in a 0.10 micron technology. The cores have private first-level caches, and share an on-chip 3.5 MB 7-way set-associative L2 cache. At 0.10 micron, this cache will occupy an area just under half the die size of the Pentium 4. All the cores are assumed to run at 2.1 GHz. This is the frequency at which an EV6 core would run if its 600 MHz, 0.35 micron implementation was scaled to a 0.10 micron technology. In the Alpha design, the amount of work per pipe stage was relatively constant across processor generations [24,31, 35,40]; therefore, it is reasonable to assume they can all be clocked at the same rate when implemented in the same technology (if not as designed, processors with similar characteristics certainly could). The input voltage for all the cores is assumed to be 1.2 V.

Table II summarizes the configurations that were modeled for various cores. All architectures are modeled as accurately as possible, given the parameters in Table II, on a highly detailed instruction-level simulator. However, we did not faithfully model every detail of each architecture; we were most concerned with modeling the approximate spaces each core covers in our complexity/performance continuum.

The various miss penalties and L2 cache access latencies for the simulated cores were determined using CACTI [80]. Memory latency was set to be 150 ns.

|                 |            | COR        | ES             |                              |

|-----------------|------------|------------|----------------|------------------------------|

| Processor       | EV4        | EV5        | EV6            | EV8-                         |

| Issue-width     | 2          | 4          | 6 (000)        | 8 (000)                      |

| I-Cache         | 8 KB, DM   | 8 KB, DM   | 64 KB, 2-way   | 64 KB, 4-way                 |

| D-Cache         | 8 KB, DM   | 8 KB, DM   | 64 KB, 2-way   | 64 KB, 4-way                 |

| Branch Pred.    | 2 KB,1-bit | 2 K-gshare | hybrid 2-level | hybrid 2-level (2X EV6 size) |

| Number of MSHRs | 2          | 4          | 8              | 16                           |

TABLE II CONFIGURATION OF THE CORES USED FOR POWER EVALUATION OF HETEROGENEOUS MULTI-

|      | FOWER AND AR | EA STATISTICS      | OF THE ALPHA CO | KE5    |

|------|--------------|--------------------|-----------------|--------|

| Core | Peak-power   | Core-area          | Typical-power   | Range  |

|      | (W)          | (mm <sup>2</sup> ) | (W)             | (%)    |

| EV4  | 4.97         | 2.87               | 3.73            | 92-107 |

| EV5  | 9.83         | 5.06               | 6.88            | 89-109 |

| EV6  | 17.80        | 24.5               | 10.68           | 86-113 |

| EV8- | 92.88        | 2.36               | 46.44           | 82-128 |

TABLE III Power and Area Statistics of the Alpha Cores

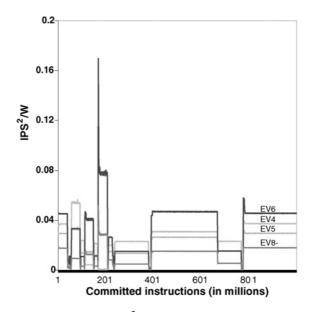

**3.3.4.2 Modeling Power.** Modeling power for this type of study is a challenge. We need to consider cores designed over the time span of more than a decade. Power depends not only on the configuration of a processor, but also on the circuit design style and process parameters. Also, actual power dissipation varies with activity, though the degree of variability again depends on the technology parameters as well as the gating style used.

No existing architecture-level power modeling framework accounts for all of these factors. Current power models like Wattch [25] are primarily meant for activitybased architectural level power analysis and optimizations within a single processor generation, not as a tool to compare the absolute power consumption of widely varied architectures. Therefore we use a hybrid power model that uses estimates from Wattch, along with additional scaling and offset factors to calibrate for technology factors. This model not only accounts for activity-based dissipation, but also accounts for the design style and process parameter differences by relying on measured datapoints from the manufacturers. Further details of the power model can be found in [60].

Table III shows our power and area estimates for the cores. As can be seen from the table, the EV8- core consumes almost 20 times the peak power and more than 80 times the real estate of the EV4 core. The table also gives the derived typical power for each of our cores. Also shown, for each core, is the range in power demand for the actual applications run, expressed as a percentage of typical power.